# WARSAW UNIVERSITY OF TECHNOLOGY

DISCIPLINE OF SCIENCE AUTOMATIC CONTROL, ELECTRONICS, ELECTRICAL ENGINEERING AND SPACE TECHNOLOGIES FIELD OF SCIENCE ENGINEERING AND TECHNOLOGY

# Ph.D. Thesis

Michał Kruszewski, M.Sc.

Functional Bus Description Language

Supervisor Wojciech Zabołotny, Ph.D., D.Sc

WARSAW 2023

# Abstract

Bus and register management is one of the crucial aspects of ASIC, SoC or FPGA based designs. The problems related to it are well known, and multiple tools or approaches are already trying to solve or mitigate them. However, all available solutions share the same register-centric paradigm. A user defines registers and then manually lays out the data into the registers. Such an approach has its limitations. A description does not contain information on data spanning multiple registers or data forming a broader context, procedure arguments, for example. It also does not contain information on the data purpose. As a result, the generated access code is low-level and usually needs an extra wrapper, which leaves room for potential human mistakes. For instance, it is the user's responsibility to guarantee proper access order to registers or to provide an atomic change of data wider than single register width.

The thesis proposes a new approach, the functionality-centric approach. In the functionalitycentric approach user defines the data with the type of its functionality. The registers and bus hierarchy are later implicitly inferred. By defining the functionality of the data placed in the registers, it is possible to generate more access code, increase code robustness, improve system design readability, and shorten the implementation process.

The thesis includes the specification of the new domain-specific language (Functional Bus Description Language), the reasoning for some of the design decisions as well as some of the compiler implementation details.

**Keywords**: bus interface, code maintenance, computer languages, control interface, design automation, design verification, documentation generation, electronic design automation, EDA, electronic systems, Functional Bus Description Language, FBDL, hardware design, hardware description language, HDL, hierarchical register description, memory, programming, register addressing, register synthesis, software generation, system management

# Streszczenie

Zarządzanie magistralą oraz rejestrami jest jednym z kluczowych aspektów podczas projektowania układów ASIC, SoC lub systemów wykorzystujących układy FPGA. Problemy z tym związane są dobrze znane. Istnieje wiele narzędzi oraz sposobów postępowania, które starają się je rozwiązywać lub niwelować ich wpływ. Wszystkie dostępne rozwiązania cechuje jednak te same podejście do zagadnienia, są one zorientowane na rejestry. Użytkownik pierw definiuje rejestr, a dopiero w kolejnym kroku ręcznie rozmieszcza w nim dane. Takie podejście zawiera pewne ograniczenia. Opis rejestrów nie zawiera informacji na temat danych znajdujących się w więcej niż jednym rejestrze, czy na temat danych będących częścią jakiegoś szerszego kontekstu, jak np. argumenty procedur. Opis nie zawiera również informacji na temat funkcjonalności jakie poszczególne dane dostarczają. W rezultacie automatycznie wygenerowany kod jest niskopoziomowy i wymaga ręcznej implementacji kodu opakowującego. To z kolei przekłada się na pozostawienie miejsca na potencjalne ludzkie pomyłki. Przykładowo, to użytkownik odpowiedzialny jest za zapewnienie poprawnej kolejności dostępów do rejestrów, czy za zapewnienie atomowości zmian wartości danych, których szerokość przekracza szerokość pojedynczego rejestru.

W rozprawie zaprezentowano nowe podejście zorientowane na funkcjonalność danych. W podejściu tym użytkownik definiuje dane wraz z ich typem funkcjonalności. Na ich podstawie są następnie automatycznie generowane rejestry wraz z hierarchią magistrali. Definiowanie funkcjonalności danych pozwala na zwiększenie ilości kodu dostępowego generowanego automatycznie, i zmniejszenie ilości kodu pisanego ręcznie. To z kolei zwiększa odporność kodu na błędy, poprawia czytelność projektu i skraca czas spędzony na implementacji.

Praca obejmuje specyfikację jezyka specyficznego dla danej domeny (Język Opisu Funkcjonalnych Magistral), uzasadnienie niektórych decyzji projektowych oraz omówienie niektórych ze szczegołów implementacji kompilatora.

Słowa kluczowe: adresowanie rejestrów, automatyzacja projektowania, magistrala, generacja oprogramowania, generacja dokumentacji, hierarchiczny opis rejestrów, interfejs sterowania, język opisu sprzętu, języki programowania, magistrala, programowanie, projektowanie sprzętu, synteza rejestrów, systemy elektroniczne, utrzymanie kodu, wery-fikacja projektu, zarządzanie systemem

# Contents

| Pr       | reface          |                                                                                                   | 9         |

|----------|-----------------|---------------------------------------------------------------------------------------------------|-----------|

| 1        | Intr            | oduction                                                                                          | 12        |

|          | 1.1             | Example problem                                                                                   | 13        |

|          | 1.2             | Register-centric approach                                                                         | 14        |

|          | 1.3             | Functionality-centric approach                                                                    | 18        |

| <b>2</b> | On-             | chip interconnect architectures                                                                   | <b>24</b> |

|          | 2.1             | AMBA AXI                                                                                          | 25        |

|          | 2.2             | Wishbone                                                                                          | 28        |

|          | 2.3             | Network on Chip                                                                                   | 29        |

| 3        | Prio            | or art                                                                                            | 33        |

|          | 3.1             | airhdl                                                                                            | 35        |

|          | 3.2             | Address Generator for Wishbone                                                                    | 35        |

|          | 3.3             | AutoFPGA                                                                                          | 36        |

|          | 3.4             | Cheby                                                                                             | 37        |

|          | 3.5             | Corsair                                                                                           | 38        |

|          | 3.6             | Tools provided by FPGA vendors                                                                    | 39        |

|          | 3.7             | hdl_registers                                                                                     | 41        |

|          | 3.8             | II & CII                                                                                          | 42        |

|          | 3.9             | IP-XACT                                                                                           | 42        |

|          | 3.10            | Opentitan Register Tool                                                                           | 43        |

|          | 3.11            | Register Wizard                                                                                   | 43        |

|          | 3.12            | RgGen                                                                                             | 43        |

|          | 3.13            | SystemRDL                                                                                         | 44        |

|          | 3.14            | vhdMMIO                                                                                           | 44        |

|          | 3.15            | wbgen 2 $\ldots$ | 45        |

| 4        | $\mathbf{Diss}$ | ertation                                                                                          | 54        |

|          | 4.1             | Thesis                                                                                            | 54        |

|          | 4.2             | Aim and scope                                                                                     | 54        |

| <b>5</b> | Fun             | ctionalities                                                                                      | 55        |

|    | 5.1   | Block                                                                                                                                      |   |     |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

|    | 5.2   | Bus                                                                                                                                        |   | 55  |

|    | 5.3   | Config                                                                                                                                     |   | 57  |

|    | 5.4   | $Irq \ldots \ldots$ |   | 58  |

|    | 5.5   | Mask                                                                                                                                       |   | 59  |

|    | 5.6   | Memory                                                                                                                                     |   | 60  |

|    | 5.7   | Param                                                                                                                                      |   | 63  |

|    | 5.8   | Proc                                                                                                                                       |   | 64  |

|    | 5.9   | Return                                                                                                                                     |   | 64  |

|    | 5.10  | Static                                                                                                                                     |   | 65  |

|    | 5.11  | Status                                                                                                                                     | • | 66  |

|    | 5.12  | Stream                                                                                                                                     | • | 66  |

| 6  | Abs   | ent features                                                                                                                               |   | 67  |

|    | 6.1   | Double side writable data                                                                                                                  |   | 67  |

|    | 6.2   | Enumeration type                                                                                                                           |   | 68  |

|    | 6.3   | Custom expression functions                                                                                                                |   | 70  |

|    | 6.4   | Manual addressing                                                                                                                          |   | 71  |

|    | 6.5   | Custom attributes                                                                                                                          |   | 71  |

| 7  | Imp   | ementation                                                                                                                                 |   | 72  |

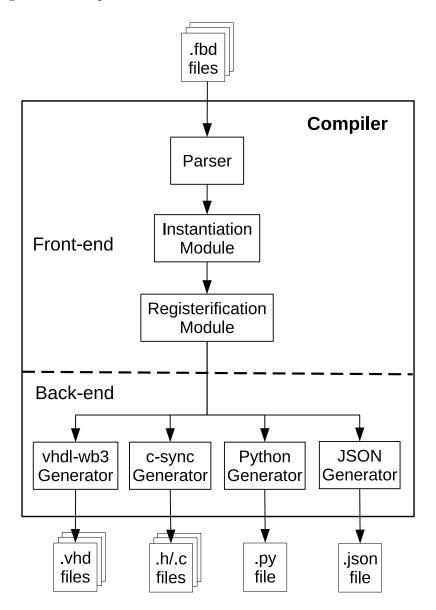

|    | 7.1   | Front-end                                                                                                                                  |   | 73  |

|    |       | 7.1.1 Parsing $\ldots$                                    |   | 74  |

|    |       | 7.1.2 Instantiation $\ldots$                              |   | 74  |

|    |       | 7.1.3 Registerification                                                                                                                    |   | 74  |

|    | 7.2   | Back-end                                                                                                                                   |   | 81  |

| 8  | Rea   | use case                                                                                                                                   |   | 86  |

| 9  | Sum   | mary                                                                                                                                       |   | 87  |

| Aj | opene | lices                                                                                                                                      |   | 97  |

| A  | Sup   | ervisor registerification results                                                                                                          |   | 98  |

| В  | Pyt]  | on code for mask access                                                                                                                    |   | 102 |

| С  | Stat  | ement from the Fluence company                                                                                                             |   | 105 |

| D  | FBI   | L Specification                                                                                                                            |   | 107 |

# List of abbreviations

- AGWB Address Generator for Wishbone

- AMBA ARM Advanced Microcontroller Bus Architecture

- **API** Application Programming Interface

- ASIC Application-Specific Integrated Circuit

- **AXI** Advanced eXtensible Interface

- **CBM** Compressed Baryonic Matter

- **CDC** Clock Domain Crossing

- **CPU** Central Processing Unit

- CMS Compact Muon Solenoid

- **DAQ** Data Acquisition

- **DESY** Deutsches Elektronen-Synchrotron

- EDA Electronic Design Automation

- EISA Extended Industry Standard Architecture

- FBDL Functional Bus Description Language

- FPGA Field Programmable Gate Array

- **GUI** Graphical User Interface

- HDL Hardware Description Language

- **HEP** High Energy Physics

- **HLS** High Level Synthesis

- HTML HyperText Markup Language

- **IP** Intellectual Property / Internet Protocol

- **ISA** Industry Standard Architecture

- JSON JavaScript Object Notation

- ${\bf LAN}\,$  Local Area Network

LSB Least Significant Bit

MCA Micro Channel Architecture

MCU Microcontroller Unit

MMIO Memory Mapped Input Output

NoC Network on Chip

**PCIe** Peripheral Component Interconnect Express

**POSIX** Portable Operating System Interface for UNIX

${\bf SLR}\,$  Super Logic Region

SoC System on Chip

**STS** Silicon Tracking System

SystemRDL System Register Description Language

**TCP** Transmission Control Protocol

TOML Tom's Obvious, Minimal Language

**UART** Universal Asynchronous Receiver-Transmitter

**URL** Uniform Resource Locator

**UVVM** Universal VHDL Verification Methodology

**USB** Universal Serial Bus

${\bf UVM}\,$  Universal Verification Methodology

**VESA** Video Electronics Standards Association

VHDL Very High Speed Integrated Circuit Hardware Description Language

${\bf W\!AN}\,$  Wide Area Network

XML Extensible Markup Language

YAML YAML Ain't Markup Language

# Preface

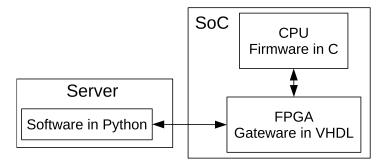

#### Context and motivation of the dissertation

Designing, implementing, and integrating FPGA-based designs with a software stack running on a traditional CPU or with a firmware stack running on an MCU poses a relatively complex technological, organizational, and methodical task. DAQ systems for HEP experiments, among military, medical, and digital entertainment systems, are good examples of areas where such tasks are omnipresent and inevitable.

The author of the dissertation, for four years, has been taking part in the design and implementation process of the gateware, firmware, and software for the DAQ system for the CBM [1] experiment that has been prepared at the GSI Helmholtzzentrum für Schwerionenforschung in Darmstadt [2].

Design environments for DAQ systems in HEP experiments are very peculiar. The whole design and implementation take relatively long, from a few to even a dozen or so years. The engineering teams are international. The educational background is varied. There are physicists, electronics engineers, computer science engineers, system administrators, etc. The spectrum of the age of the members is vast, ranging from first-year Ph.D. students to halftime retired workers. Most members participate in multiple projects or have academic duties, so the time they devote to a particular task is limited. During the development phase, there is also a rotation of the employees. As a whole system is extensive and complex and must work reliably, it is natural that the preliminary prototypes vary significantly from the final solutions. All of this leads to implementing the same or similar functionalities multiple times. For example, a change of programming language after the prototyping stage forces such reimplementation.

During the first two years of the studies, the author explored how to make such complex and multidimensional projects more manageable and verifiable. Trying to incorporate some industrial methodologies, such as UVM framework or formal verification, simply failed. There were at least several reasons for this. To name a few:

- Lack of free, open source tools or limited functionality of such tools. Paid commercial tools have expensive licenses.

- Too steep learning curve and lack of learning resources. The EDA tools appear to be inadequate for engineers who do not use them every day for eight hours. Instead

of focusing on the design and fundamental problems, one spends time learning how to use the EDA tools, and each of them has distinct user interface.

Throughout the work, it turned out that in such a diverse environment, there is another policy suited much better. Instead of incorporating cumbersome industrial standards that need expensive licenses, one can automatically generate as much gateware, firmware, and software as possible. As long as the description format, based upon which parts of the system are generated, is easily readable by a human, the work is moving forward surprisingly fast.

Based on this observation, the author has been looking for a way to enhance and extend existing generic methods and tools commonly used for gateware, firmware, and software code generation. During the work on the AGWB [3], and after using it for a few months, the author noticed that a relatively lot of code was still repeatedly implemented manually. That manually implemented code had some common characteristics and could be easily automatically generated. The only thing missing to generate it was the information on the functionality that must be served by a given data. That required shifting the accent from the register (register-centric approach) to the data, or more precisely to the functionality of the data (functionality-centric approach). After analysing state-of-the-art tools and approaches, the author concluded that there is actually no solution based on the data functionality paradigm. The author has decided that the idea is worth trying, and the FBDL realizes this idea.

#### Structure of the thesis

The thesis consists of 9 chapters and 4 additional appendices. Appendix D is the specification of the newly defined Functional Bus Description Language. It is advised to at least skim it before reading the dissertation and later come back to it while reading the chapter 5. The specification also includes definitions of some terms used in the thesis.

Chapter 1 introduces the bus and register management problem. It provides a simplified example that is used to present some of the subproblems and analyze how they are solved in the register-centric (typical) approach and functionality-centric (newly proposed) approach.

Chapter 2 briefly discusses on-chip interconnect architectures. It uses AMBA AXI and Wishbone buses to present two distinct bus control logics. It also discusses the NoC technology, a natural progression of traditional on-chip buses.

Chapter 3 is the prior art analysis. It includes only solutions following the register-centric paradigm. The author proposes a shift of paradigm to the functionality, and no solution

following this approach has been found.

Chapter 4 contains the definition of the thesis. Then, the aim and scope of the dissertation is described.

Chapter 5 serves as an extension to the FBDL specification. It discusses all supported functionalities, and unlike the specification, it focuses on answering the "why" questions instead of the "how" questions. It is recommended to read subsections of this chapter concurrently with the corresponding subsections of the FBDL specification (first specification, then dissertation) or to read the whole specification first.

Chapter 6 discusses the most common features present in the register-centric tools but absent in the FBDL. The focus is on reasoning why they are absent at the current stage of the language.

Chapter 7 describes the implementation of the compiler for the FBDL. As the comprehensive description would be relatively long and would include aspects irrelevant from the thesis point of view, the chapter describes only the overall structure and focuses on some general details that probably any FBDL compliant compiler will have to face.

Chapter 8 provides information on the project in which FBDL has been used. However, due to the proprietary nature of the project, no internal details are revealed.

Chapter 9 summarizes the advantages of describing a system bus using the functionalitycentric approach instead of the register-centric.

The thesis has numerous code snippets and listings used as examples to illustrate problems better or explain solutions. The VHDL language has been chosen for the gateware, and the Python language has been chosen for the software. However, all presented concepts are programming language agnostic, so any language could be selected, and the reasoning would remain valid.

# **1** Introduction

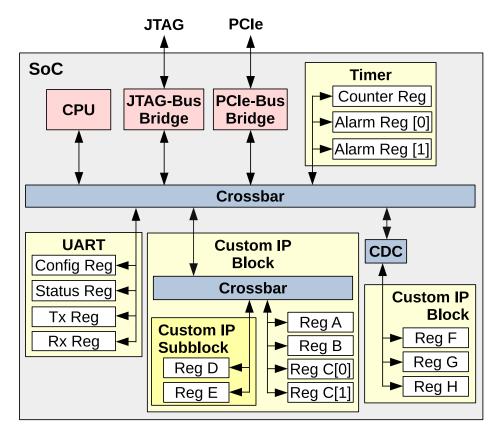

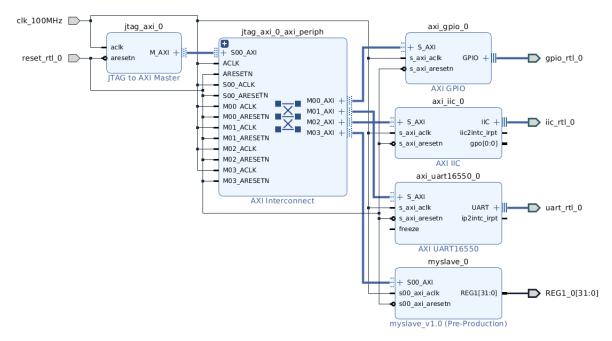

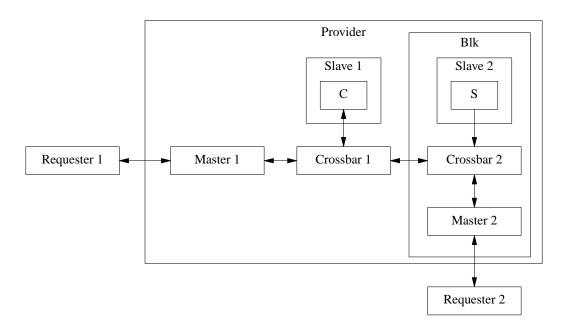

Most ASIC, FPGA, or SoC designs, for sure the more complex ones, have some kind of internal bus. Such a bus is often referred to as a "system bus", "local bus", "on-chip bus", "interconnect bus" or "on-chip interconnect bus" (the last one is the most formal and probably the most appropriate). The main role of the bus is to provide an organized and structured manner for connecting independent modules within the chip. It also serves as some kind of gateway to access the internals of the gateware or hardware design from the firmware or software stack. Such access includes writing control signals, reading status signals, bi-directional data streaming, procedure triggering, interrupt signaling, etc. Figure 1.1 presents an example simplified structure of some SoC. Master modules are red, slave modules are yellow, and bus fabric components are blue.

Figure 1.1: Example internal structure of some SoC design with bus.

A bus usually consists of an address bus, a data bus, and a control bus. The most popular on-chip buses used in FPGA designs are probably AXI [4] (which is part of the AMBA) and Wishbone [5]. If there is a bus in a design, then the bus needs to be managed. The bus management consists of the following logical elements:

- 1. Address space management. This includes:

- a) Assigning address ranges to the modules.

- b) Aligning address ranges according to the user's policy.

- 2. Bus fabric management. This includes:

- a) Description of the modules hierarchy.

- b) Generation of the bus fabric components (such as crossbars) according to the user-provided description.

- 3. Registers management. This includes:

- a) Ordering registers within the modules.

- b) Splitting long signals between multiple registers.

- c) Grouping short signals into a single register.

- d) Attributing additional functions to the registers, such as associated strobe or acknowledgment signals.

All of the bus management tasks can be done manually, in a semi-automated way, or in a fully automated way. The greater the automation, the less room for potential engineers' mistakes and the greater pace of the project development.

Managing the bus in a complex system is a well-known and non-trivial problem, especially in hardware-software co-design projects [6, 7, 8, 9]. Even though various approaches and implementations have already been proposed, there is still no solution that would make the bus management process fully automated. All available tools and standards either only support some of the logical elements of bus management or require users to do the register management manually. The register management is the most time-consuming and error-prone part of the bus management.

## 1.1 Example problem

The following section introduces an example to ease the reasoning. The example is also used to present the typical register-centric approach for managing registers and the new functionality-centric approach proposed in the thesis. It presents some, but not all, problems encountered in a register-centric approach that are eliminated in the newly proposed approach.

Let's assume there is a module implemented in the FPGA logic called the *Supervisor*. The Supervisor is capable of scheduling work to be done by some *Worker* modules. The Supervisor has its own 48 bits internal counter that can be reset. The Supervisor can pass data to Worker modules at programmed counter value. There are 24 workers, and the data passed to them is two 12 bits long vectors. The data might be passed to any set of workers. For simplicity, let's assume that the data passed to all the workers is the same. The Supervisor also has two additional status bits, informing whether it is currently programmed (the data is scheduled to be processed) and whether it has been programmed in the past. Programming in the past means that the Supervisor can also be unprogrammed. Listing 1 shows the VHDL interface of the example Supervisor. Signals connected to the particular ports have analogous names without the \_i, \_o suffixes.

The example Supervisor must be controlled by the software running on a CPU. Listing 2 shows an example Python interface of the Supervisor.

Inside an FPGA, there is a 32 bits wide bus (this is the width of the data; the width of the address is irrelevant in this consideration). What bus it is and how it can be accessed from the software is irrelevant to the analysis. A proper interface for accessing the bus is provided via the registers\_handle parameter.

### 1.2 Register-centric approach

In the register-centric approach, one has to take the following mandatory steps:

- a) Identify control signals. In the case of the Supervisor, these are: reset\_counter, program, unprogram, programmed\_counter\_value, worker\_data0, worker\_data1, workers\_mask.

- b) Identify status signals. In the case of the Supervisor, these are: counter, programmed , programmed\_in\_past, workers\_ready.

- c) Identify which control signals form a broader context. For instance, worker\_data0 does not make any sense when it is used alone. It is solely one of the procedure's parameters allowing for passing data to the workers. On the other hand, unprogram makes sense on its own.

- d) Identify which status signals form a broader context. There is no such case in the

```

entity Supervisor is

generic (WORKER_COUNT : positive := 24);

port (

clk_i : in std_logic;

-- Supervisor control interface

: out std_logic_vector(47 downto 0);

counter_o

reset_counter_i : in std_logic;

-- Program procedure

: in std_logic;

program_i

programmed_counter_value_i : in std_logic_vector(47 downto 0);

: in std_logic_vector(11 downto 0);

worker_data0_i

: in std_logic_vector(11 downto 0);

worker_data1_i

-- Workers mask is set independently

workers_mask_i : in std_logic_vector(WORKER_COUNT-1 downto 0);

-- Unprogram procedure

unprogram_i : in std_logic;

-- Status bits

programmed o

: out std_logic;

programmed_in_past_0 : out std_logic;

workers_ready_o : out std_logic_vector(WORKER_COUNT-1 downto 0);

-- Interface to Workers

workers_ready_i : in std_logic_vector(WORKER_COUNT-1 downto 0);

data_valid_o : out std_logic_vector(WORKER_COUNT-1 downto 0);

worker_data0_o : out std_logic_vector(11 downto 0);

worker_data1_o : out std_logic_vector(11 downto 0)

);

end entity;

```

Listing 1: Example Supervisor VHDL module interface.

example Supervisor.

- e) Calculate the number of bits needed for control and status signals. The example Supervisor needs 82 status bits (counter, programmed, programmed\_in\_past, workers\_ready) and 96 control bits (programmed\_counter\_value, worker\_data0, worker\_data1, workers\_mask). Whether reset\_counter, program, unprogram should be included is yet another question. As these are single-bit signals solely triggering some action, they can be implemented as registers or fields requiring explicit set and clear, or as register-associated signals triggered during register write. The second option is usually better as it provides lower latency. However, if the first option is chosen, then there are 99 control bits.

- f) Identify control and status signals needing special handling. For example, in the

```

class Supervisor():

def __init__(self, registers_handle):

pass

def read_counter(self):

pass

def reset_counter(self):

pass

def read_status_bits(self):

pass

def program(self, counter_value, worker_data0, worker_data1):

pass

def unprogram(self):

pass

def read_workers_ready(self):

pass

def set_workers(self, workers):

pass

```

Listing 2: Example Supervisor Python software interface.

case of the Supervisor there is 48 bits long **counter** value. As the bus width is 32 bits, one needs to provide some mechanism for an atomic read of the counter value to keep the value integrity while reading the counter.

g) Manually decide the register layout. This step involves answering a lot of irrelevant questions. For example, how many registers are needed? Should lower bits of the counter value be placed in the first or the second status register? Should reading the first or the second register of the counter value trigger the atomic read? Should programmed and programmed\_in\_past be placed in separate registers or in one of the counter value registers to save some address space size? What should be the order of control signals within the control registers? The number of possible implementations is infinite.

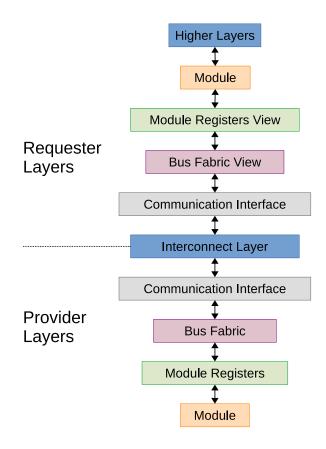

Quite a lot of work, even for such a simple module. Moreover, the whole register structure must also be reflected in the software. Figure 1.2 shows a conceptual model of layers in a register-centric approach. The communication interface and interconnect layers are irrelevant in terms of the address space and registers management. Register-centric solutions focus on the module registers and bus fabric layers. They allow describing one or more of these layers and can auto-generate appropriate gateware, firmware, and software. However, these solutions ignore that some signals might need special handling or be a part of some broader context. For instance, a user has to implement atomic reads or writes himself. The same applies to the software responsible for triggering procedures

Figure 1.2: Conceptual stack of layers in the register-centric approach.

implemented in the gateware, consisting of multiple control registers. Such an approach is error-prone and leads to duplication of information. For example, the information that some signal needs atomic read is manually implemented in two places, in the firmware source code, and in the software source code.

Working manually on the register layout is also fragile to changes. In the example Supervisor module, there are 96 bits needed for the control signals if reset\_counter, program , unprogram are implemented as strobe signals associated with given control registers. This is exactly three registers on a 32 bits wide bus. However, should reset\_counter , program, unprogram be associated with registers storing some data, or maybe with virtual registers (registers with addresses but not storing any data)? What happens if more workers have to be added? The user has to manually add more control registers and adjust the firmware and software accordingly. Yet another question arises. Should the whole, longer workers\_mask be moved to the new third control register, or maybe just the new extra bits?

Listing 3 shows an example implementation of the software handling Supervisor module in the case of a register-centric approach. It all has to be coded manually. What is worse, in case of any register changes it also has to be adjusted manually. This is because available solutions are register-centric. They treat registers as a goal, not as a path to an actual goal, which is always the functionality of the data.

The register-centric approach gives much freedom and is highly flexible. On the other hand, it does not look at the registers from the broader context and is unaware of the semantics of the data stored in them. This implies micro-management of registers, generates a lot of irrelevant questions, and is relatively fragile to changes.

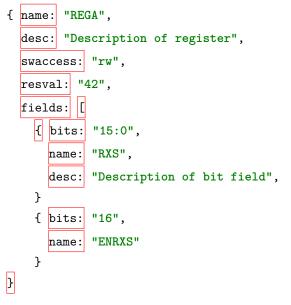

Listing 4 presents an example SystemRDL description for example Supervisor. System-RDL is the only formally defined register-centric format. If there was a need to increase the number of workers above the bus width, then the description would need a relatively lot of adjustments. The register layout is described manually, so the WORKER\_COUNT macro can no longer be used. Listing 5 presents the file difference that would have to be applied in such a case.

# **1.3 Functionality-centric approach**

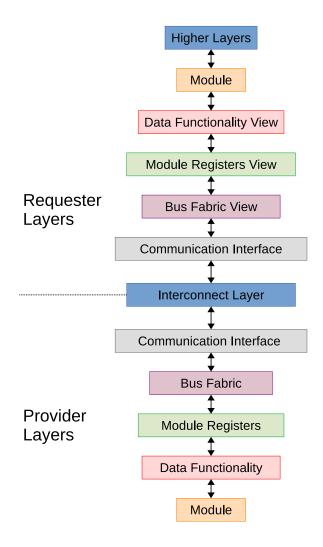

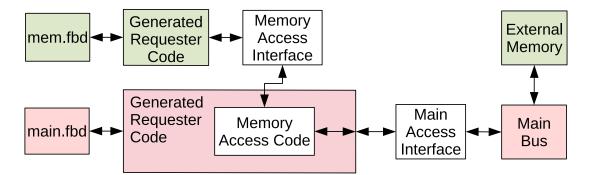

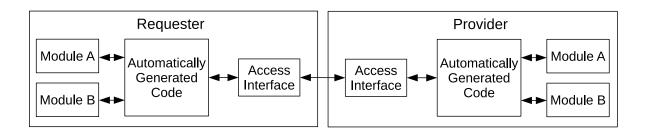

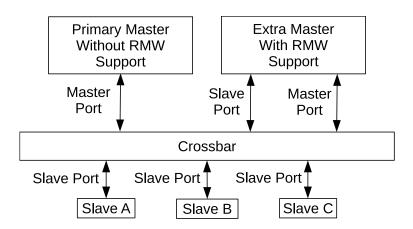

The thesis proposes a shift of paradigm leading to a different approach. It looks at the design and modules from the *functionality* point of view. It is the functionality of the data that is in the center. An engineer always thinks about the functionality a given module should serve. The whole register layout is automatically generated based on the declarative description of the provided functionalities. Figure 1.3 shows a conceptual model of layers in the functionality-centric approach. There is an extra data functionality layer compared to the register-centric approach. This is the core layer in this model. The module register layers are automatically generated based on the data functionality layer.

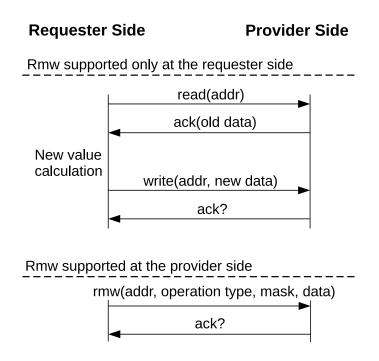

Looking at data from the functionality point of view allows for avoiding register micromanagement. Having functionality embedded into the register data notation also helps to prevent information duplication. For example, atomic accesses or procedure calls can be easily automatically generated for both the requester and the provider. This removes a whole surface of potential human mistakes.

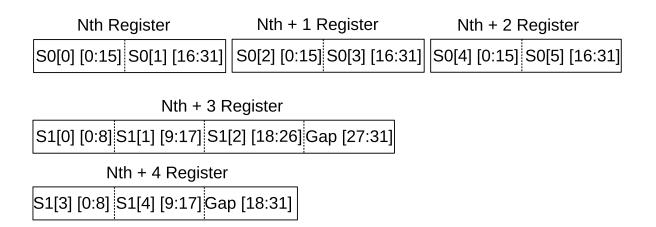

Listing 6 presents FBDL description for example Supervisor, and appendix A presents registerification results. If there was a need to change the number of workers, then it would be enough to change the WORKER\_COUNT constant value, even if the new number was greater than the bus width. Listing 7 presents the file difference that would have to be applied in such a case. As the registerification process is carried out automatically by

Figure 1.3: Conceptual stack of layers in the functionality-centric approach.

the compiler also the whole register layout is automatically adjusted. There is no need to adapt gateware, firmware or software code manually. As FBDL promotes safety by default, there is also no need to declare **Counter** status to be atomic explicitly. Any data wider than bus width has atomic access unless the user explicitly resigns from it.

```

class Supervisor:

def __init__(self, registers_handle):

self.registers_handle = registers_handle

def read counter(self):

""" To keep counter integrity and perform atomic read, the

counter register 0 must be read as the first one. """

counter = self.registers_handle.Counter0.read()

counter |= self.registers_handle.Counter1.read() << 32</pre>

return counter

def reset counter(self):

self.registers_handle.Reset_Counter.write(0)

def read_status_bits(self):

""" Returns tuple (programmed, programmed_in_past). """

status = self.registers_handle.Status.read()

return status & 1, status & 2

def program(self, counter_value, worker_data0, worker_data1):

""" ProgramO register has to be written as the last one, as it has

strobe signal associated with it, which serves as the arm signal. """

self.registers_handle.Program2.write((worker_data1 << 12) | worker_data0)</pre>

self.registers_handle.Program1.write(counter_value >> 32)

self.registers_handle.ProgramO.write(counter_value & OxFFFFFFF)

def unprogram(self):

self.registers_handle.Unprogram.write(0)

def read_workers_ready(self):

return self.registers_handle.Workers_Ready.read()

def set_workers(self, workers):

""" Enable given workers. Workers argument can be a worker number

or a list of workers numbers. """

if type(workers) == int:

workers = [workers]

mask = 0

for w in workers:

mask |= 1 \ll w

self.registers_handle.Workers_Mask.write(mask)

```

Listing 3: Example Supervisor software interface implementation in the case of a registercentric approach.

```

addrmap Supervisor {

name = "Supervisor";

default regwidth = 32;

`define WORKER COUNT 24

reg empty_strobe_reg_t {

field {sw = w; hw = na; swacc;} dummy;

}:

// CounterO has to be read as the first one to

// keep counter value integrity.

reg { field { sw = r; hw = w; } data; } Counter0;

reg {

regwidth = 16;

field {sw = r; hw = w;} data[16];

} Counter1;

empty_strobe_reg_t Reset_Counter;

reg {

field {fieldwidth = `WORKER_COUNT; sw = w; hw = r;} mask;

} Workers_Mask;

// ProgramO must be written as the last one,

// as the write triggers Program procedure.

reg {

field {sw = w; hw = r; swacc;} counter value0;

} Program0;

reg {

regwidth = 16;

field {sw = w; hw = r;} counter_value1[16];

} Program1;

reg {

field {sw = w; hw = r;} worker_data0[12];

field {sw = w; hw = r;} worker data1[12];

} Program2;

empty_strobe_reg_t Unprogram;

reg {

field {fieldwidth = `WORKER_COUNT; sw = r; hw = w;} mask;

} Workers Ready;

reg {

field {fieldwidth = 1; sw = r; hw = w;} programmed;

field {fieldwidth = 1; sw = r; hw = w;} programmed in past;

} Status;

};

```

Listing 4: Example Supervisor SystemRDL description.

```

5,6d4

`define WORKER_COUNT 24

<

<

19,20c17,21

<

field {fieldwidth = `WORKER_COUNT; sw = w; hw = r;} mask;

} Workers_Mask;

<

_ _ _ .

field {sw = w; hw = r;} mask;

>

} Workers_Mask0;

>

reg {

>

>

field {fieldwidth = 1; sw = w; hw = r;} mask;

} Workers_Mask1;

>

37,38c38,42

field {fieldwidth = `WORKER_COUNT; sw = r; hw = w;} mask;

<

} Workers Ready;

<

_ _ _

field {sw = r; hw = w;} mask;

>

} Workers_Ready0;

>

reg {

>

field {fieldwidth = 1; sw = r; hw = w;} mask;

>

} Workers_Ready1;

>

```

Listing 5: Example Supervisor SystemRDL description change for workers count increase above the bus width.

```

Main bus

Supervisor block

const WORKER_COUNT = 24

Counter status; width = 48

Reset_Counter proc

Workers Mask mask; width = WORKER COUNT

Program proc

counter_value param; width = 48

worker data

[2] param; width = 12

Unprogram proc

Workers_Ready status; width = WORKER_COUNT

type status_t status; width = 1; groups = "status"

status t

programmed

programmed_in_past status_t

```

Listing 6: Example Supervisor FBDL description.

3c3 < const WORKER\_COUNT = 24 ----> const WORKER\_COUNT = 33

Listing 7: Example Supervisor FBDL description change for workers count increase above the bus width.

# 2 On-chip interconnect architectures

Probably every practical computing system ever created consists of independent components (there is at least some processing unit and a memory). In order to achieve synergy and serve desired functionality, these components must communicate with each other using a set of organized rules (communication protocols or standards). This network of connections is often referred to as system interconnect. The very first interconnect architectures were also called buses. The term "bus" originates from the computer, whose history can be traced back to 1946 [10]. This term is still in common use, although nowadays, bus protocols differ significantly from their ancestors. A bus, in general, is a common pathway through which information flows from one computer component to another. In the early days, computer components were relatively big, and all buses were physically made of copper wires, or later as traces on the printed circuit boards. Initially, those buses served four functions:

- 1. Data sharing the primary purpose of every bus. Data processing is the core concept of every computing system. It would not be achievable without data transfer between system components.

- 2. Addressing a bus had address lines. This allowed data to be sent to a particular system component to a specific memory location.

- 3. Clock distribution a bus provided a system clock signal to synchronize the peripherals attached to it or even to clock the peripheral itself.

- 4. Power supplying a bus supplied power to various peripherals connected to it.

The most popular computer expansion buses include ISA [11], EISA [12], MCA [13], VESA [14], SCSI [15], USB [16], and PCI/PCIe [17]. Most of them are not used anymore as they have been replaced with the USB and PCIe. With the advancement of technology, especially integrated circuits technology, it was possible to shrink components of computing systems to the sizes allowing placing multiple of them (or even the whole system) on a single chip. There was still a need to connect system components to enable communication between them. However, traditional microcomputer buses were fundamentally handicapped for use as a SoC interconneciton. This is because they were designed to drive long signal traces and connector system which are highly inductive and capacitive. In this regard, SoC is much simpler and faster. Furthermore, the SoC solutions have a rich set of interconnection resources. These do not exist in microcomputer buses because they are limited by chips packaging and mechanical connectors. As the existing buses were not optimal for implementation on chips, the interconnect architectures started to be grouped into two classes, the off-chip interconnect architectures, and the on-chip interconnect architectures. The on-chip buses serve the same functions as the off-chip buses except the last one, the power supplying [18]. In the case of SoCs, the power is usually supplied separately via the chip backbone. The clock is also not always distributed, as a bus can be asynchronous [19], but this might also be valid in the case of off-chip buses. Examples of prevailing on-chip buses include ARM AMBA AXI [4], IBM CoreConnect [20], Intel Avalon [21], STMicroelectronics STBus [22], Opencores Wishbone [5], MARBLE (asynchronous) [23].

The following two sections briefly describe two on-chip bus standards, the AXI and the Wishbone. They have been chosen because:

- 1. they are omnipresent and popular,

- 2. they have different control logic.

The descriptions are brief because Wishbone revision B4 specification has 128 pages and AMBA AXI specification is 273 pages long, and the subsections' purpose is solely to introduce example bus logic.

#### 2.1 AMBA AXI

The AMBA AXI protocol is copyrighted by the Arm company. Its first version was released in 2003, and its latest version 5 was released in March 2023. In 2021 the specification changed primary terminology, the Master term was replaced with the Manager term, and the Slave term was replaced with the Subordinate term. It is worth mentioning because almost all available materials, except the specification, and available IP cores still use the old terminology. AXI gained a lot of popularity probably because it became de facto the standard for connecting IP cores in FPGA designs utilizing AMD Xilinx or Intel chips. Both companies are the major programmable logic devices market vendors and both offer AXI interconnect cores as well as functional IP cores with AXI interface.

The AXI protocol defines five independent channels:

- 1. write request (AW),

- 2. write data (W),

- 3. write response (B),

- 4. read requist (AR),

- 5. read data (R).

Request channels carry control information that describes the nature of the data to be transferred. Having independent channels for write and read means that the master can simultaneously write and read the same slave. Write throughput is not limited by read transactions, and read throughput is not limited by write transactions. This is not true, for example, for the Wishbone bus.

The specification does not impose possible system interconnect topologies and only mentions the most popular ones:

- 1. shared request and data channels,

- 2. shared request channel and multiple data channels,

- 3. multilayer, with multiple request and data channels.

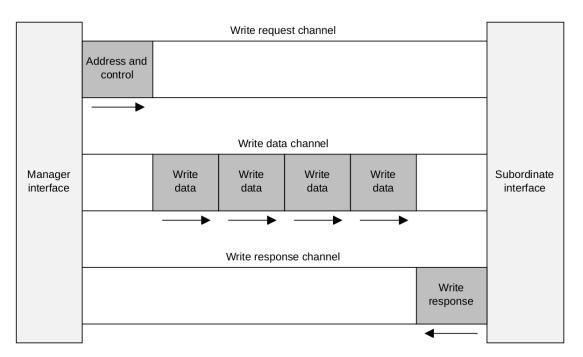

Figure 2.1 presents AXI channel architecture of writes. A single transaction might contain multiple transfers. Write transaction completion is signaled only for a complete transaction, not for each data transfer in a transaction.

Figure 2.1: AXI channel architecture of writes [4].

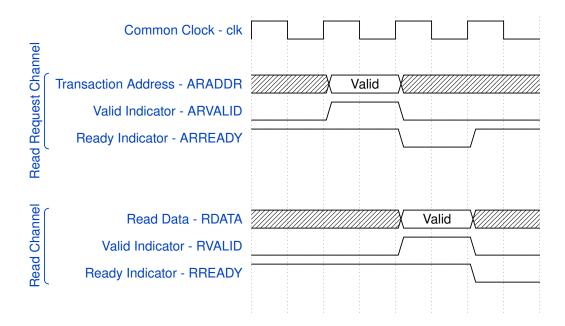

Figure 2.2 shows the timing diagram for AXI single read transaction with single data transfer and a bare minimum number of interface signals. It is the simplest possible transaction with the minimum number of channels involved. The manager drives address

Figure 2.2: AXI single read transaction with single data transfer.

and valid signals in the read request channel and the ready signal in the read channel. The subordinate drives the ready signal in the read request channel and data and valid signals in the read channel. The side driving the ready signal can assert or deassert it anytime, even before valid signal assertion. This means handshaking in AXI can take as little as one clock cycle. A transfer occurs only when both the valid and ready signals are high. The side driving the valid signal must wait for ready assertion after it asserts the valid signal. A deadlock happens if the side driving the valid signal waits for the ready signal assertion before the valid signal assertion and the side driving the ready signal waits for the valid signal assertion before the ready assertion. To prevent such scenarios, the specification states that the valid signal source is not permitted to wait until the ready signal is asserted before asserting the valid signal. The specification forbids combinatorial paths between input and output signals, both on the manager and subordinate sides.

The AMBA AXI specification also defines the AXI-Lite version of the protocol. The AXI-Lite is a subset of AXI where all transactions have one data transfer. It is intended for communication with register-based components and simple memories when bursts of data transfer are not advantageous.

There is also AMBA AXI-Stream protocol defined in the separate specification [24]. AXI-Stream is a point-to-point protocol connecting a single Transmitter and a single Receiver. The terms Master/Manager and Slave/Subordinate are not used in this case, as the data always flows from the Transmitter to the Receiver. The specification of AXI-Stream describes how data is transferred but does not describe the meaning of the data. AXI-Stream is often used in data streaming applications, for example, video processing. Although defined as a separate protocol, the AXI-Stream utilizes the same valid-ready handshaking approach as the standard AXI protocol.

## 2.2 Wishbone

Wishbone bus architecture was developed by Silicore Corporation. It was put into the public domain in August 2002 by OpenCores (an organization promoting open IP cores development). Wishbone versions till revision 4 were not copyrighted, and revision 4 is copyrighted to the OpenCores. Wishbone can be freely copied and distributed.

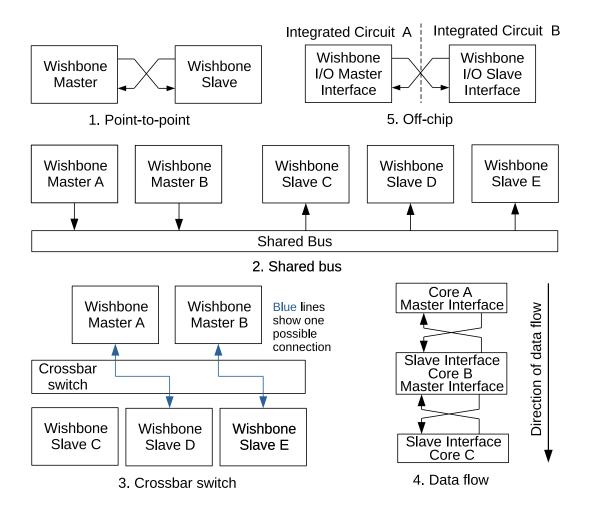

Wishbone supports various core interconnection means, including:

- 1. point-to-point,

- 2. shared bus,

- 3. crossbar switch,

- 4. data flow,

- 5. off chip.

The possible interconnections are presented in Figure 2.3.

Wishbone supports single read/write transactions, with possible pipelining (introduced in revision 4), block read/write transactions, and read-modify-write transactions. It also supports registered feedback transactions which allow for better throughput.

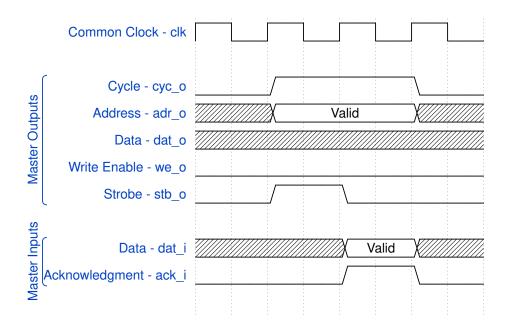

Figure 2.4 shows the timing diagram for a classic standard single read transaction with the bare minimum number of interface signals. It is the simplest possible transaction. However, it is enough to present how fundamentally different Wishbone control logic is from the AXI control logic. The transaction starts when the cycle signal is asserted by the master on the second clock rising edge. The master also drives the address bus, write enable and asserts the strobe signal to inform the slave that signals are valid and can be read. The slave drives data on the third clock rising edge and asserts the acknowledgment signal to inform the master that data is valid. The slave may wait before asserting the acknowledgment signal in order to throttle the transaction speed.

Compared to the AXI, the handshaking in Wishbone is related to the transaction as a whole. There is no separate handshaking for requests, data, and write response.

Figure 2.3: Possible Wishbone interconnections.

# 2.3 Network on Chip

The network on chip is an on-chip interconnect architecture trying to overcome the limits of the traditional bus architectures. The problem was observed and reported in the late 1990s, and was initially addressed in the early years of the 21st century [25, 26, 27, 28]. The most popular drawbacks of the traditional bus architectures that NoC tries to solve include:

- 1. Limited bandwidth shared by all attached units.

- 2. Decrease of the maximum frequency with the increase of the number of modules connected to the bus. Every module adds parasitic capacitance, therefore the electrical performance degrades with the increase of modules number.

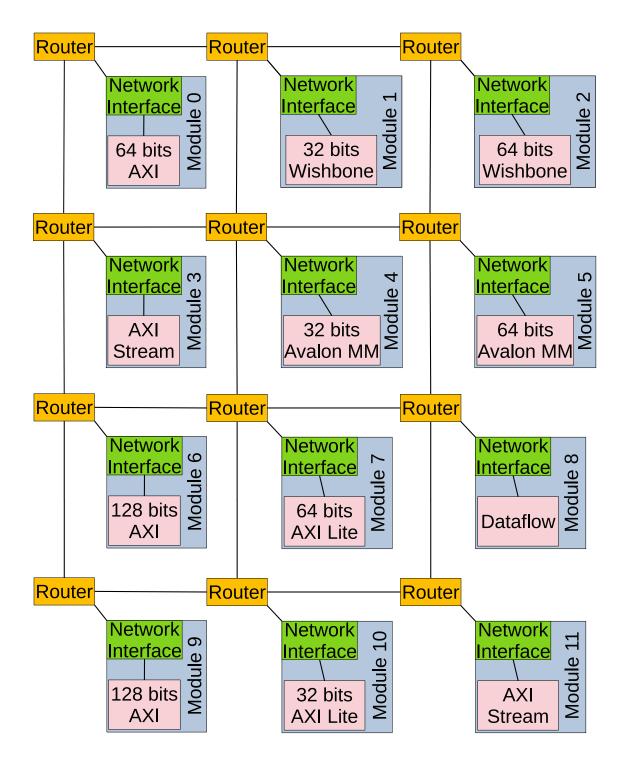

- 3. IPs interface incompatibility. The 32 bits AXI Lite master will simply not work with the 64 bits Wishbone slave in a traditional bus architecture without an extra bridge. In the NoC approach each network node can have an individual interface

Figure 2.4: Wishbone classic standard single read transaction.

for local registers access.

4. Coupled transaction, transport, and physical activities. Changes to the bus physical implementation can have serious ripple effects upon the implementation of the higher-level bus behaviors. NoC distinguishes transaction, transport, and physical layers that can be adjusted or improved independently.

However, NoC is mainly used in cases of high bandwidth performance critical heterogeneous SoC applications. Even homogeneous designs focused on accelerating the processing of gigabytes or terabytes of data (usually implemented using HLS technique) do not use NoC, but rather different types of AXI interfaces depending on the nature and amount of data being exchanged between modules [29]. This is because NoC is not free of drawbacks. The most popular ones are:

- 1. Latency increase due to the internal network connections and routing algorithms.

- 2. Increased resource utilization compared to the traditional bus architectures.

- 3. Increased overall system complexity.

There are numerous different NoC topologies [30, 31, 32, 33, 34, 35]. The most popular ones include: ring, octagon, star, mesh, torus, folded torus, butterfly, binary tree, fat tree, cube, crossed cube, hypercube, reduced hypercube, reduced mesh and cluster-based hybrid, mesh connected ring, cmesh.

Although the NoC architecture was inspired by well-known computer networks such as LAN or WAN, it differs significantly from them. This is because the implementation of the

protocols used in these networks, such as IP [36] or TCP [37], would consume a relatively large amount of resources and would require significant buffering capabilities. NoC packet typically consists of a header and payload data. The header must include at least the address of the destination node, but it often also includes data length, data tags, and the address of the source node. How the data is routed via the network depends on the routing algorithm. Although the macro-level architecture of the NoC differs significantly from the traditional bus architecture, the packet data still has to be somehow distributed inside the module attached to the network via the network interface. There are two standard ways to achieve this. The first one is dataflow communication, and the second one is address space communication. This is exactly what traditional buses were designed for. So, in the end, the traditional bus architectures are still used within the NoC architectures. However, their scope is limited to the single network nodes. Figure 2.5 presents an example 12 nodes network on chip with the mesh topology.

Figure 2.5: Example 12 nodes mesh network on chip.

# 3 Prior art

This chapter presents the current state of the art. The term "tool" is used for all solutions, although not all are strictly tools. Moreover, some are standalone entities, while others are a part of more extensive tools. Each tool has been designed and implemented by different teams. Although their main goal is the same, they sometimes put an accent on diverse areas. As a result, relative comparison is not always straightforward. This is why they are rather matched against a generic template. Nonetheless, none of the available solutions offers a functional view of data placed in the registers. They are registers-centric. The description of each tool is prepended with a table summarizing its capabilities. The order of analysis is alphabetical.

It is important to mention that all described tools and solutions are in continuous development, so some of their features might have changed, or new features might have been added since they were described. It is also worth mentioning that if tool T claims support for feature F or language L, then it might not be a full support, as all such tools are implemented in an incremental fashion. It does not indicate the weakness of the tools, but rather shows a pragmatic approach to the problem. There would be no technical progress in the described field if the tools were usable only when they were 100 % complete.

Table 3.1 presents the result of the review of existing solutions. Comparing bus and register management tool features is a challenging task. First of all, none of the registercentric tools, except SystemRDL, has formal specification. The implementation is the specification. What is more, most of the tools target only a limited set of hardware description or programming languages, and they are usually tailored to these languages. Comparing features of FBDL with register-centric tools is also not straightforward, as FBDL is functionality-centric and has a different paradigm. For example, some of the tools allow data value range constraining. However, it works only for data fitting a single register, whereas in FBDL, it works for data of any width. Partial support means that a given feature is available only to some extent. For example, tools utilizing YAML [38] format support parametrization achieved using YAML syntax. However, they do not provide any extra parametrization mechanism, and full design parametrization is not possible solely with YAML inheritance.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             | airhdl | airhdl AGWB | AutoFPGA Cheby Corsair | Cheby |   | FPGA<br>Vendors | hdl_registers | II<br>& CII | IP-XACT | Opentitan<br>Register<br>Tool | Register<br>Wizard | RgGen | SystemRDL | OIIMMbdv | wbgen2 | FBDL |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------|-------------|------------------------|-------|---|-----------------|---------------|-------------|---------|-------------------------------|--------------------|-------|-----------|----------|--------|------|

| Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Register<br>Requires Fields | Y      | N           | Z                      | N     | Y | n               | Y             | N           | N       | Y                             | Z                  | Y     | Y         | Z        | Y      | N    |

| M       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit-fields                  | Y      | Υ           | γ                      | Υ     | Υ | Y               | Υ             | Υ           | Υ       | γ                             | Y                  | Y     | Y         | γ        | Υ      | Υ    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Hierarchy<br>Description    | Z      | Y           | Y                      | Y     | Z | Y               | N             | Y           | Y       | N                             | z                  | Z     | Y         | Z        | Z      | Y    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Design<br>Parametrization   | Ь      | Y           | Y                      | Ь     | Ч | Ь               | Z             | Y           | Y       | N                             | Z                  | Ь     | Υ         | Ь        | N      | Y    |

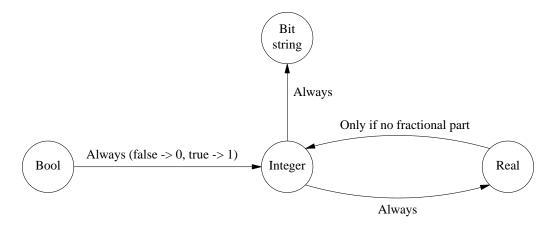

| X       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y <thy< th=""> <thy< th=""> <thy< th=""></thy<></thy<></thy<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interrupts                  | Y      | N           | Y                      | N     | n | Y               | Ь             | z           | Υ       | γ                             | Y                  | Ь     | Y         | γ        | Υ      | Υ    |

| N         Y         N         Y         N         Y         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Memory                      | Y      | Y           | γ                      | Υ     | z | Y               | z             | Υ           | Υ       | γ                             | N                  | Y     | Y         | N        | Υ      | Υ    |

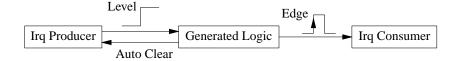

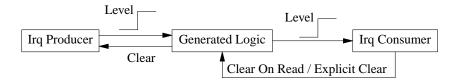

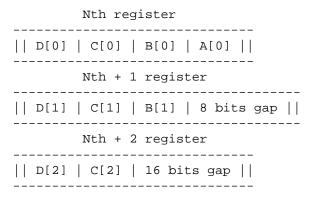

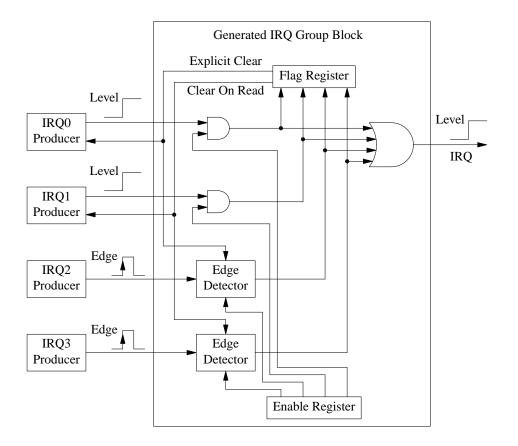

| N       Y       Y       Y       Y       Y       Y       Y         N       Y       Y       Y       Y       Y       Y       Y         N       Y       Y       Y       Y       Y       Y       Y         Y       Y       Y       Y       Y       Y       Y       Y         Y       Y       Y       Y       Y       Y       Y       Y       Y         Y       Y       Y       Y       Y       Y       Y       Y       Y       Y         Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y         Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y         Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Constants                   | z      | Y           | γ                      | Z     | Υ | z               | Y             | Y           | Υ       | Y                             | z                  | z     | Z         | N        | Z      | Υ    |